# ISD1700 Series Design Guide

October 2006 Revision 0

# **TABLE OF CONTENTS**

| 1 | GENERAL DESCRIPTION                   | 6  |

|---|---------------------------------------|----|

| 2 | FEATURES                              | 7  |

| 3 | BLOCK DIAGRAM                         | 8  |

| 4 | PINOUT CONFIGURATION                  | 9  |

| 5 | PIN DESCRIPTION                       | 10 |

| 6 | FUNCTIONAL DESCRIPTION                | 14 |

|   | 6.1 Detailed Description              |    |

|   | 6.1.1 Audio Quality                   | 14 |

|   | 6.1.2 Message Duration                | 14 |

|   | 6.1.3 Flash Storage                   | 14 |

|   | 6.2 Memory Array Architecture         | 14 |

|   | 6.3 Modes of Operations               | 16 |

|   | 6.3.1 Standalone (Push-Button) Mode   | 16 |

|   | 6.3.2 SPI Mode                        | 16 |

| 7 | ANALOG PATH CONFIGURATION (APC)       | 17 |

|   | 7.1 APC Register                      | 17 |

|   | 7.2 Device Analog Path Configurations | 18 |

| 8 | STANDALONE (PUSH-BUTTON) OPERATIONS   | 19 |

|   | 8.1 Sound Effect (SE) Mode            | 19 |

|   | 8.1.1 Sound Effect (SE) Features      | 19 |

|   | 8.1.2 Entering SE Mode                | 19 |

|   | 8.1.3 SE Editing                      | 19 |

|   | 8.1.4 Exiting SE Mode                 | 20 |

|   | 8.1.5 Sound Effect Duration           | 20 |

|   | 8.2 Operation Overview                | 20 |

|   | 8.2.1 Record Operation                | 21 |

|   | 8.2.2 Playback Operation              | 22 |

|   | 8.2.3 Forward Operation               | 22 |

|   | 8.2.4 Erase Operation                 | 23 |

|   | 8.2.5 Reset Operation                 | 25 |

|   | 8.2.6 VOL Operation                   | 26 |

|   | 8.2.7 FT (Feed-Through) Operation     | 26 |

|   | 8.3 vAlert Feature (Optional)         | 26 |

|    | 8.4 Analog Inputs                               | 26 |

|----|-------------------------------------------------|----|

|    | 8.4.1 Microphone Input                          |    |

|    | 8.4.2 Analn Input                               | 27 |

|    | 8.5 System Management                           | 27 |

| 9  | CIRCULAR MEMORY ARCHITECTURE (CMA)              | 28 |

|    | 9.1 Restoring Circular Memory Architecture      |    |

| 10 | SERIAL PERIPHERAL INTERFACE (SPI) MODE          | 31 |

|    | 10.1 Microcontroller Interface                  |    |

|    | 10.2 SPI Interface Overview                     | 31 |

|    | 10.2.1SPI Transaction Format                    | 31 |

|    | 10.2.2MOSI Data Format                          | 32 |

|    | 10.2.3MISO Data Format                          | 33 |

|    | 10.3 SPI Command Overview                       | 34 |

|    | 10.4 Switching from SPI mode to Standalone Mode | 35 |

|    | 10.5 ISD1700 Device Registers                   | 35 |

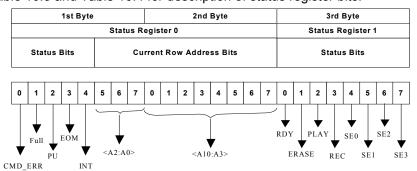

|    | 10.5.1Status Register 0 (SR0)                   | 35 |

|    | 10.5.2Status Register 1 (SR1)                   | 37 |

|    | 10.5.3APC Register                              | 37 |

|    | 10.5.4Playback Pointer (PLAY_PTR)               | 38 |

|    | 10.5.5Record Pointer (REC_PTR)                  | 38 |

|    | 10.5.6DEVICEID Register                         | 38 |

| 11 | SPI COMMAND REFERENCE                           | 39 |

|    | 11.1 SPI Priority Commands                      | 41 |

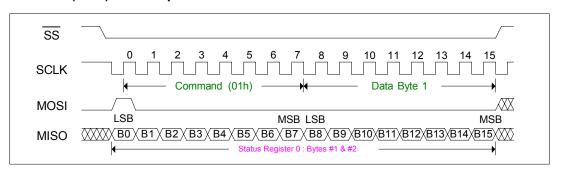

|    | 11.1.1PU (0x01) Power Up                        | 41 |

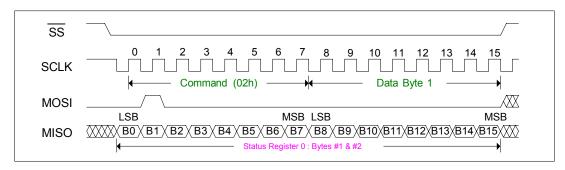

|    | 11.1.2STOP (0x02)                               | 42 |

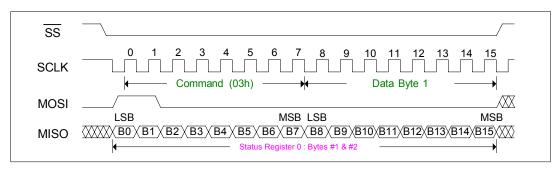

|    | 11.1.3RESET (0x03)                              | 42 |

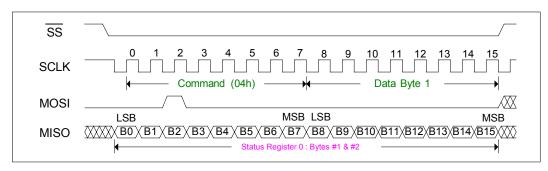

|    | 11.1.4CLR_INT(0x04)                             | 43 |

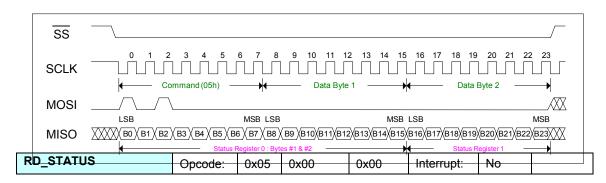

|    | 11.1.5RD_STATUS (0x05)                          | 43 |

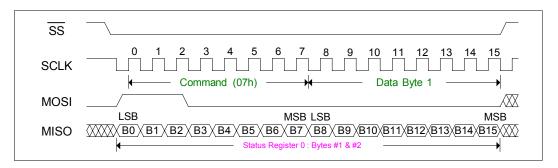

|    | 11.1.6PD (0x07) Power Down                      | 44 |

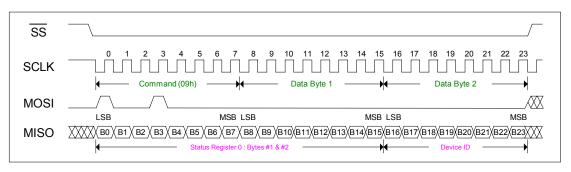

|    | 11.1.7DEVID (0x09) Read Device ID               | 45 |

|    | 11.2 Circular Memory Commands                   | 45 |

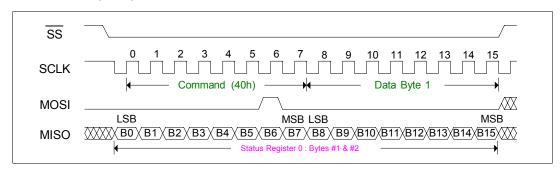

|    | 11.2.1PLAY (0x40)                               | 46 |

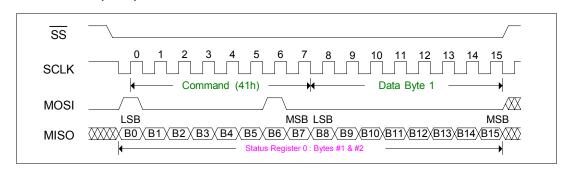

|    | 11.2.2REC (0x41)                                | 46 |

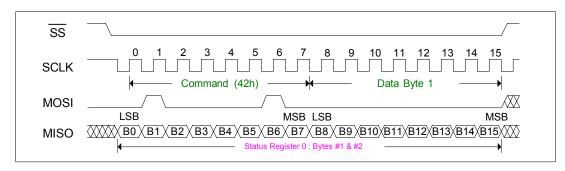

|    | 11.2.3ERASE (0x42)                              | 47 |

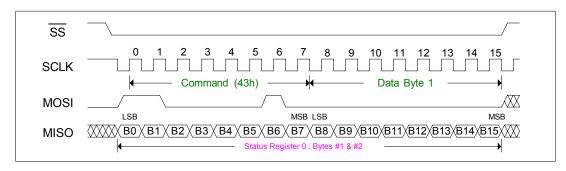

|    | 11.2.4G_ERASE (0x43) Global Erase               | 48 |

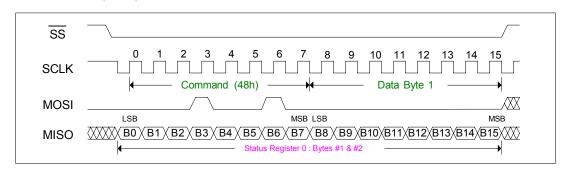

|    | 11.2.5FWD (0x48)                                                    |    |

|----|---------------------------------------------------------------------|----|

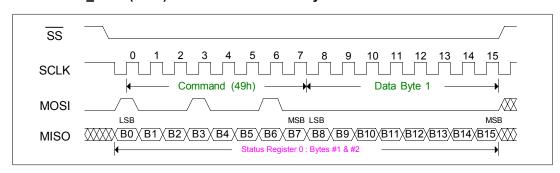

|    | 11.2.6CHK_MEM (0x49) Check Circular Memory                          |    |

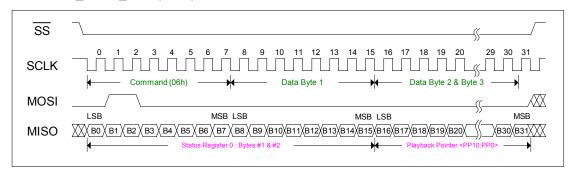

|    | 11.2.7RD_PLAY_PTR (0x06)                                            | 50 |

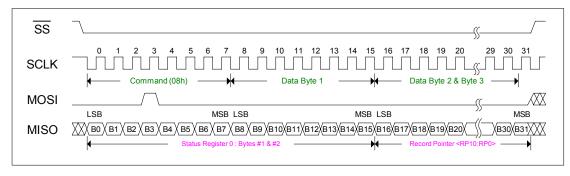

|    | 11.2.8RD_REC_PTR (0x08)                                             |    |

|    | 11.3 Analog Configuration Commands                                  | 51 |

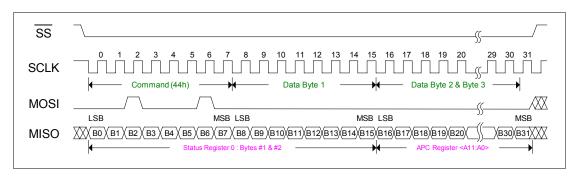

|    | 11.3.1RD_APC (0x44) Read APC Register                               | 51 |

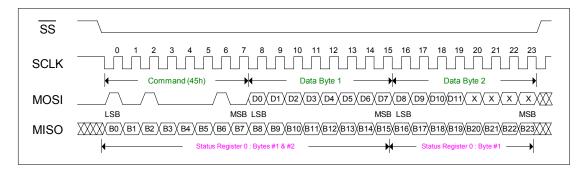

|    | 11.3.2WR_APC1 (0x45) Load APC Register                              | 51 |

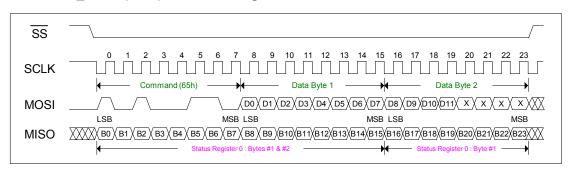

|    | 11.3.3WR_APC2 (0x65) Load APC Register                              | 52 |

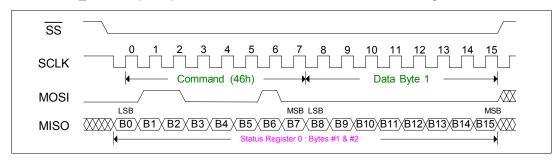

|    | 11.3.4WR_NVCFG (0x46) Write APC data into Non-Volatile Memory       | 53 |

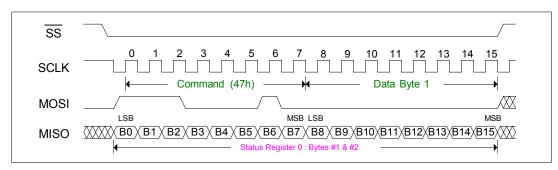

|    | 11.3.5LD_NVCFG (0x47) Load APC register from Non-Volatile Memory    | 53 |

|    | 11.4 Direct Memory Access Commands                                  | 54 |

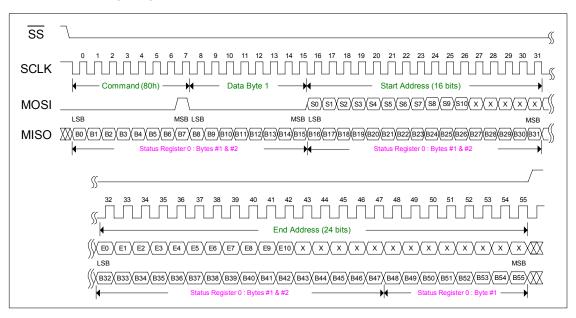

|    | 11.4.1SET PLAY (0x80)                                               | 54 |

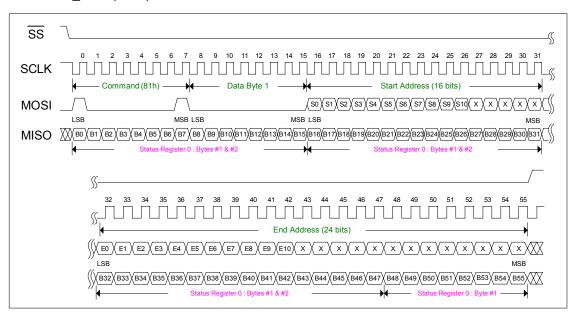

|    | 11.4.2SET_REC (0x81)                                                | 55 |

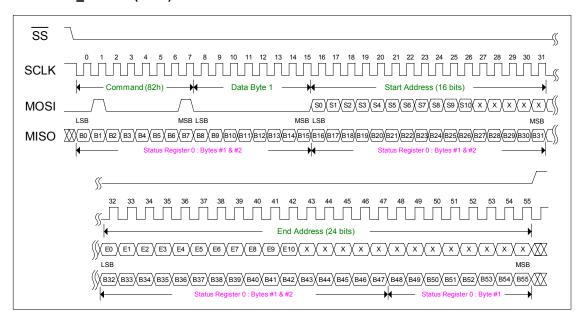

|    | 11.4.3SET_ERASE (0x82)                                              | 56 |

|    | 11.5 Additional Command                                             | 57 |

|    | 11.5.1EXTCLK (0x4A)                                                 | 57 |

|    | 11.6 General Guidelines for Writing Program Code                    | 58 |

|    | 11.7 Examples of Various Operating Sequences                        | 59 |

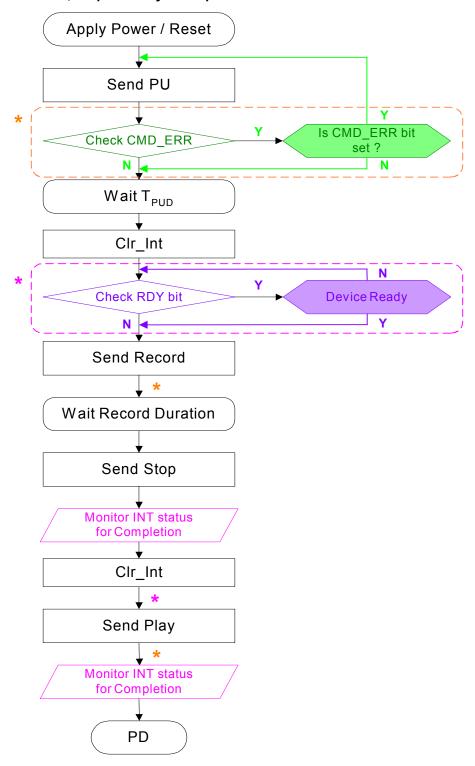

|    | 11.7.1Record, Stop and Playback operations                          | 60 |

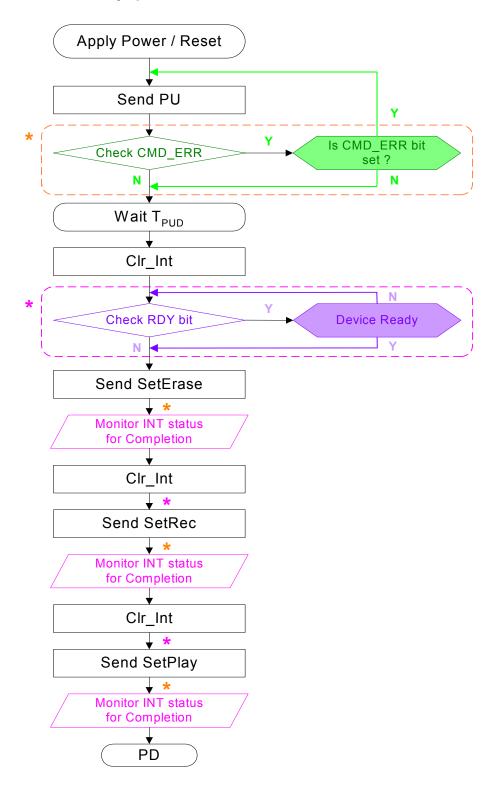

|    | 11.7.2SetRec and SetPlay operations                                 | 61 |

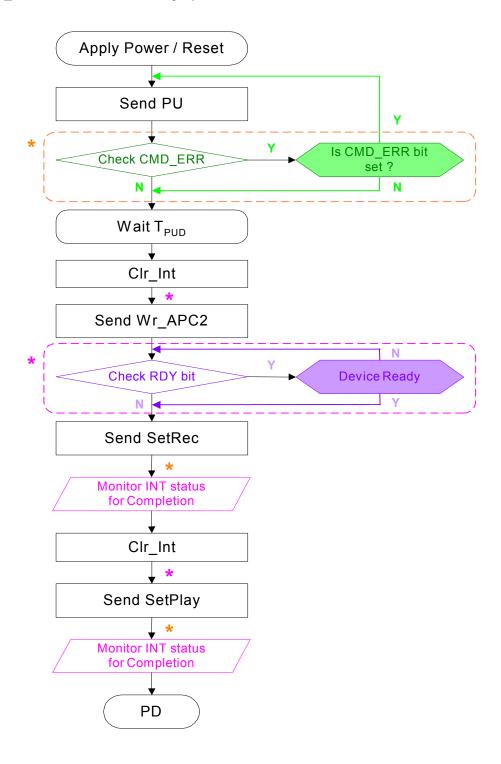

|    | 11.7.3Wr_APC2, SetRec and SetPlay operations                        | 62 |

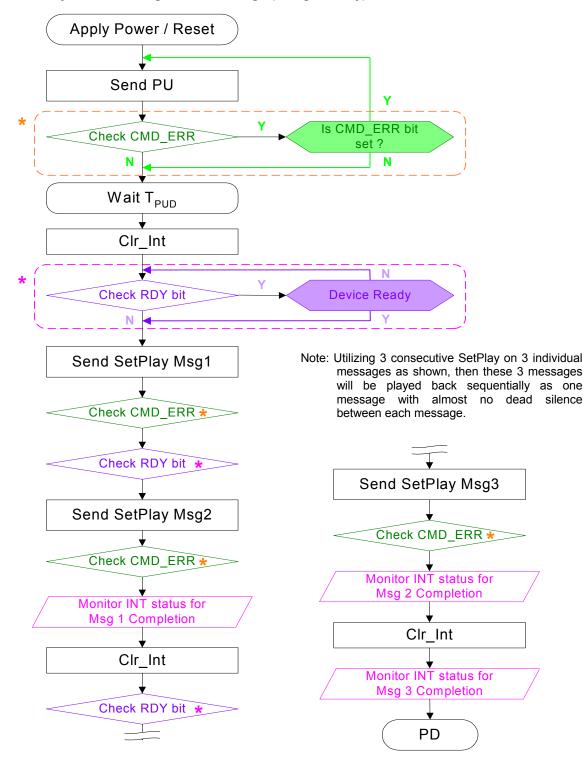

|    | 11.7.4Playback 3 Messages as 1 Message (using SetPlay)              | 63 |

| 12 | TIMING DIAGRAMS                                                     | 64 |

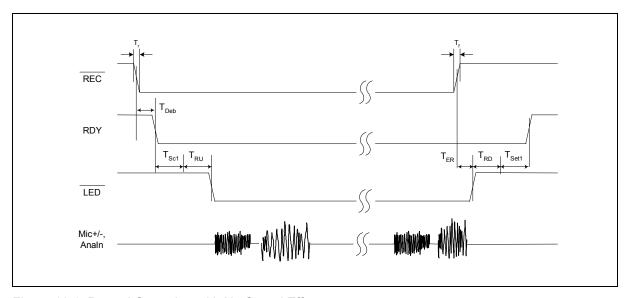

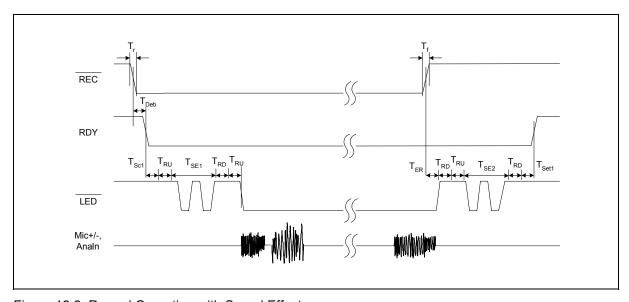

|    | 12.1 Record Operation                                               | 64 |

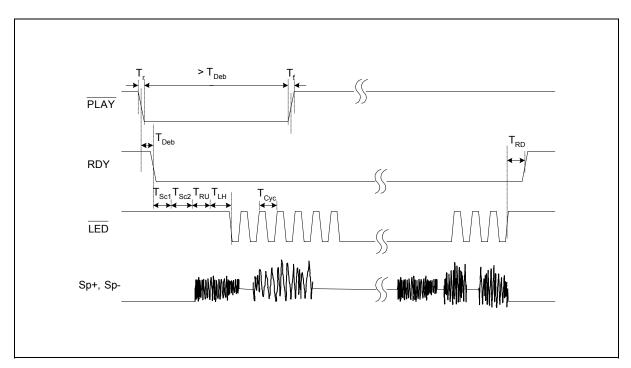

|    | 12.2 Playback Operation                                             | 65 |

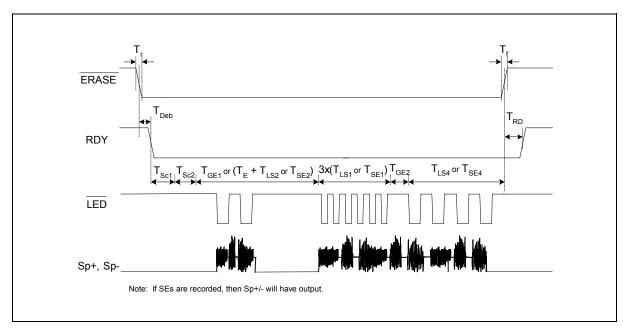

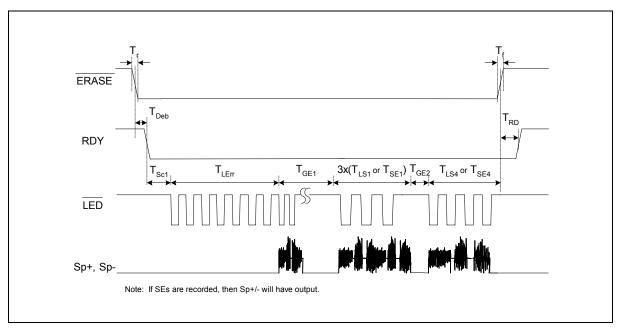

|    | 12.3 Erase Operation                                                | 66 |

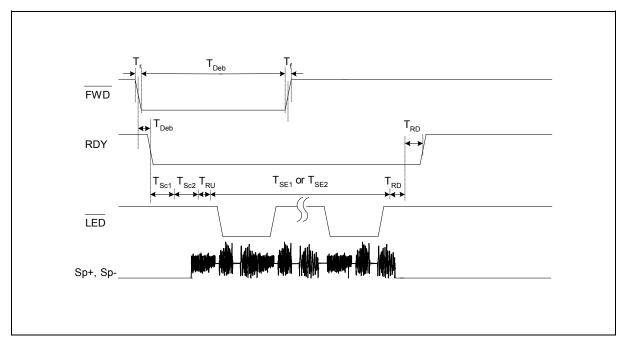

|    | 12.4 Forward Operation                                              | 67 |

|    | 12.5 Global Erase Operation                                         | 68 |

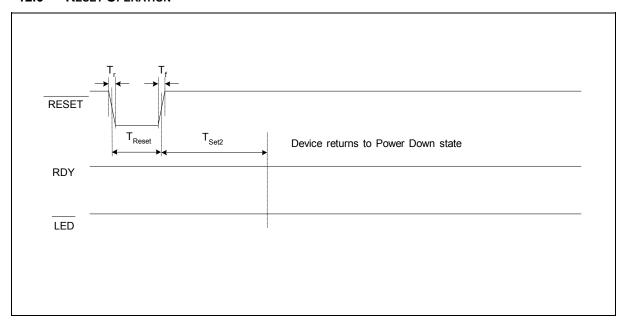

|    | 12.6 Reset Operation                                                | 68 |

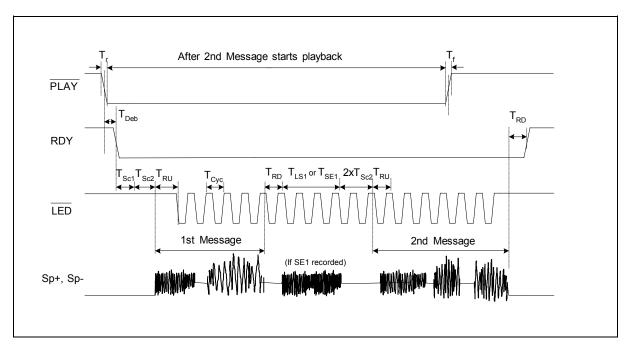

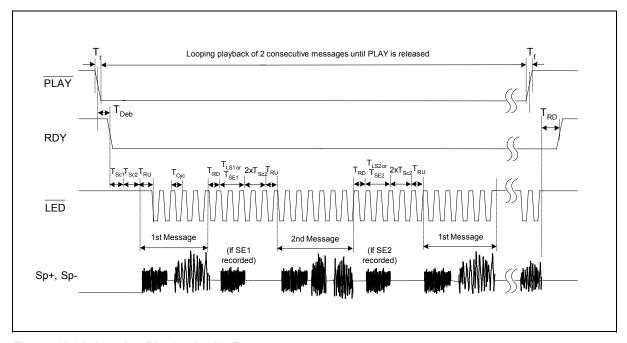

|    | 12.7 Looping Playback Operation                                     | 69 |

|    | 12.8 Global Erase Operation to Restore Circular Memory Architecture | 70 |

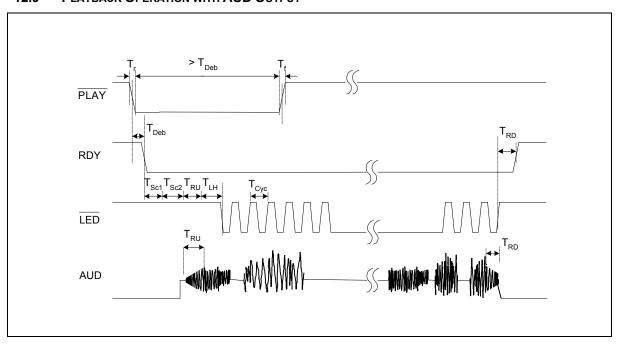

|    | 12.9 Playback Operation with AUD Ouput                              | 70 |

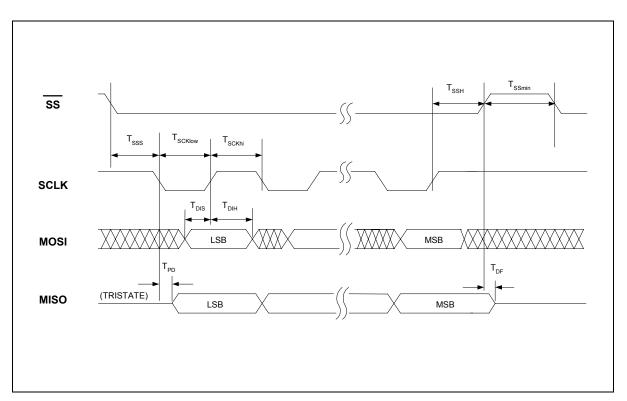

|    | 12.10 SPI Operation                                                 | 71 |

| 13 | ABSOLUTE MAXIMUM RATINGS                                            | 72 |

|    | 13.1 Operating Conditions                                           |    |

| 14 | ELECTRICAL CHARACTERISTICS       | 74 |

|----|----------------------------------|----|

|    | 14.1 DC Parameters               | 74 |

|    | 14.2 AC Parameters               | 75 |

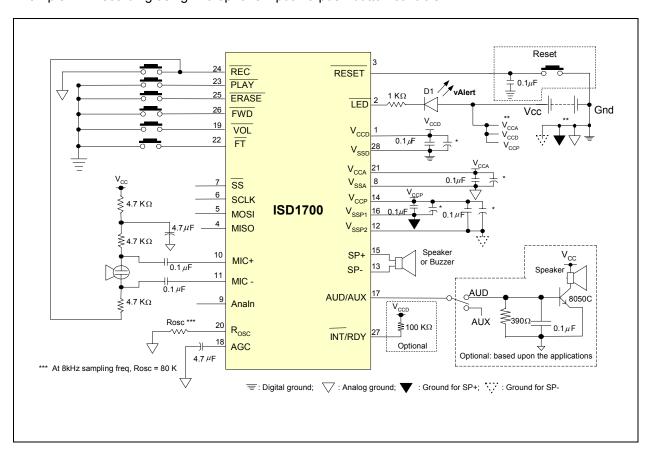

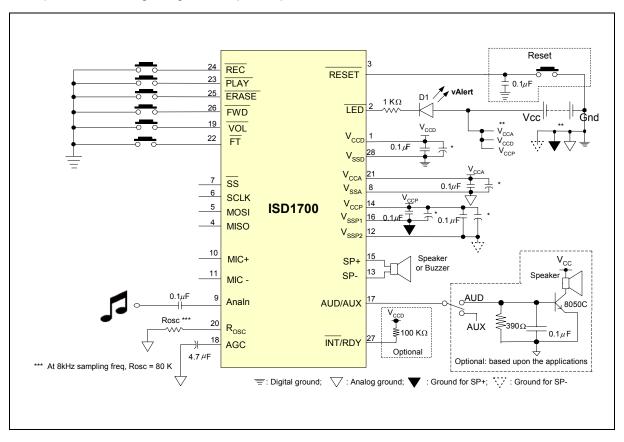

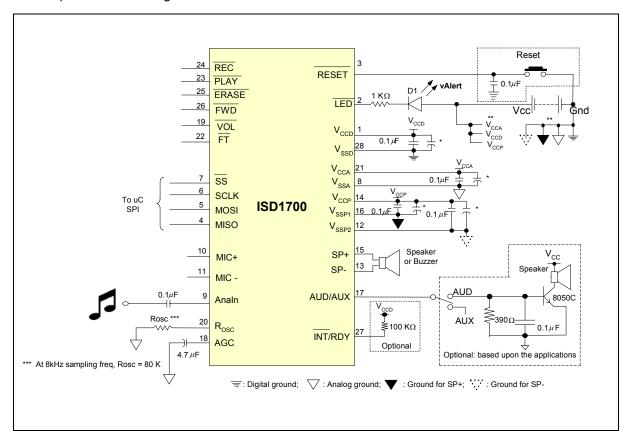

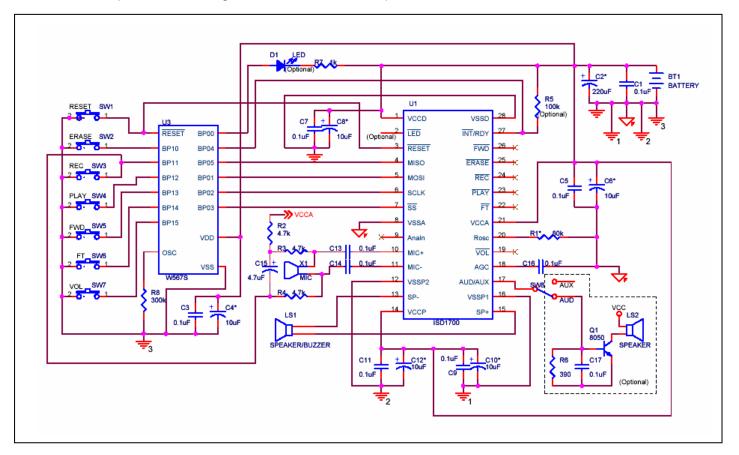

| 15 | TYPICAL APPLICATION CIRCUITS     | 76 |

|    | 15.1 Good Audio Design Practices | 79 |

| 16 | ORDERING INFORMATION             | 80 |

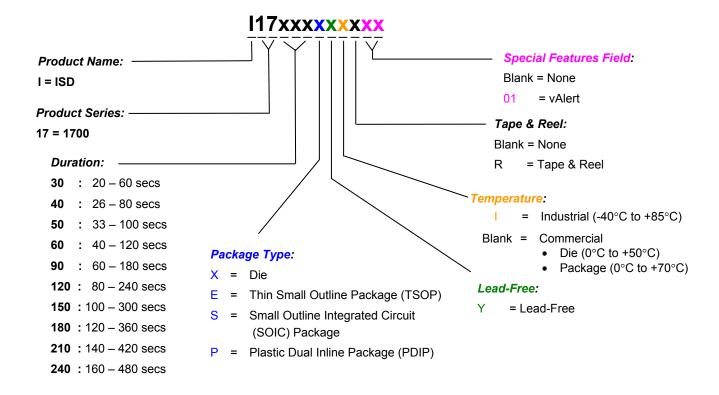

| 17 | VERSION HISTORY                  | 81 |

#### 1 GENERAL DESCRIPTION

The Winbond® ISD1700 ChipCorder® Series is a high quality, fully integrated, single-chip multi-message voice record and playback device ideally suited to a variety of electronic systems. The message duration is user selectable in ranges from 26 seconds to 120 seconds, depending on the specific device. The sampling frequency of each device can also be adjusted from 4 kHz to 12 kHz with an external resistor, giving the user greater flexibility in duration versus recording quality for each application. Operating voltage spans a range from 2.4 V to 5.5 V to ensure that the ISD1700 devices are optimized for a wide range of battery or line-powered applications.

The ISD1700 is designed for operation in either standalone or microcontroller (SPI) mode. The device incorporates a proprietary message management system that allows the chip to self-manage address locations for multiple messages. This unique feature provides sophisticated messaging flexibility in a simple push-button environment. The devices include an on-chip oscillator (with external resistor control), microphone preamplifier with Automatic Gain Control (AGC), an auxiliary analog input, antialiasing filter, Multi-Level Storage (MLS) array, smoothing filter, volume control, Pulse Width Modulation (PWM) Class D speaker driver, and current/voltage output.

The ISD1700 devices also support an optional "vAlert" (voiceAlert) feature that can be used as a new message indicator. With vAlert, the device flashes an external LED to indicate that a new message is present. Besides, four special sound effects are reserved for audio confirmation of operations, such as "Start Record", "Stop Record", "Erase", "Forward", "Global Erase", and etc.

Recordings are stored into on-chip Flash memory, providing zero-power message storage. This unique single-chip solution is made possible through Winbond's patented Multi-Level Storage (MLS) technology. Audio data are stored directly in solid-state memory without digital compression, providing superior quality voice and music reproduction.

Voice signals can be fed into the chip through two independent paths: a differential microphone input and a single-ended analog input. For outputs, the ISD1700 provides a Pulse Width Modulation (PWM) Class D speaker driver and a separate analog output simultaneously. The PWM can directly drive a standard  $8\Omega$  speaker or typical buzzer, while the separate analog output can be configured as a single-ended current or voltage output to drive an external amplifier.

While in Standalone mode, the ISD1700 devices automatically enter into power down mode for power conservation after an operation is completed.

In the SPI mode, the user has full control via the serial interface in operating the device. This includes random access to any location inside the memory array by specifying the start address and end address of operations. SPI mode also allows access to the Analog Path Configuration (APC) register. This register allows flexible configuration of audio paths, inputs, outputs and mixing. The APC default configuration for standalone mode can also be modified by storing the APC data into a non-volatile register (NVCFG) that is loaded at initialization. Utilizing the capabilities of ISD1700 Series, designers have the control and flexibility to implement voice functionality into the high-end products.

Notice: The specifications are subject to change without notice. Please contact Winbond Sales Offices or Representatives to verify current or future specifications. Also, refer to the website for any related application notes.

October 2006 - 6 - Revision 0

#### 2 FEATURES

- Integrated message management systems for single-chip, push-button applications

- o **REC**: level-trigger for recording

- PLAY: edge-trigger for individual message or level-trigger for looping playback sequentially

- o **ERASE**: edge-triggered erase for first or last message or level-triggered erase for all messages

- o FWD: edge-trigger to advance to the next message or fast message scan during the playback

- VOL: 8 levels output volume control

- RDY/INT: ready or busy status indication

- o **RESET**: return to the default state

- Automatic power-down after each operation cycle

- Selectable sampling frequency controlled by an external oscillator resistor

| Sampling Frequency | 12 kHz | 8 kHz | 6.4 kHz | 5.3 kHz | 4 kHz  |

|--------------------|--------|-------|---------|---------|--------|

| Rosc               | 60 kΩ  | 80 kΩ | 100 kΩ  | 120 kΩ  | 160 kΩ |

- Selectable message duration

- o A wide range selection from 30 secs to 240 secs at 8 kHz sampling frequency

- Message and operation indicators

- o Four customizable Sound Effects (SEs) for audible indication

- o Optional vAlert (voiceAlert) to indicate the presence of new messages

- o LED: stay on during recording, blink during playback, forward and erase operations

- Dual operating modes

- Standalone mode:

- Integrated message management techniques

- Automatic power-down after each operation cycle

- SPI mode

- Fully user selectable and controllable options via APC register and various SPI commands

- Two individual input channels

- MIC+/MIC-: differential microphone inputs with AGC (Automatic Gain Control)

- o Analn: single-ended auxiliary analog input for recording or feed-through

- · Dual output channels

- o Differential PWM Class D speaker outputs directly drives an 8 Ω speaker or a typical buzzer

- o Configurable AUD (current) or AUX (voltage) single-ended output drives external audio amplifier

- · ChipCorder standard features

- o High-quality, natural voice and audio reproduction

- o 2.4V to 5.5V operating voltage

- o 100-year message retention (typical)

- 100,000 record cycles (typical)

- Temperature options:

- Commercial: 0°C to +50°C (die); 0°C to +70°C (packaged units)

- o Industrial: -40°C to +85°C (packaged units)

- Packaging types: available in die, PDIP, SOIC and TSOP

- Package option: Lead-free packaged units

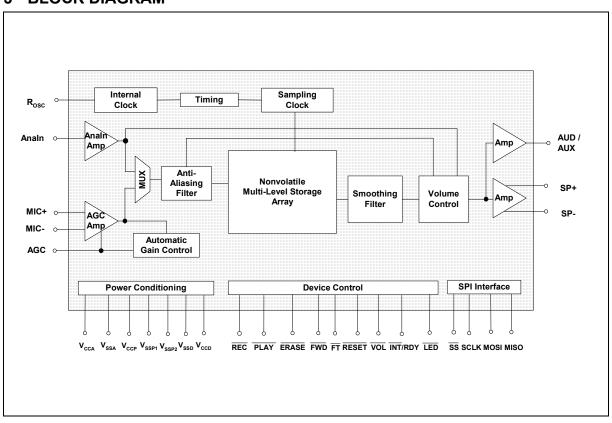

# **3 BLOCK DIAGRAM**

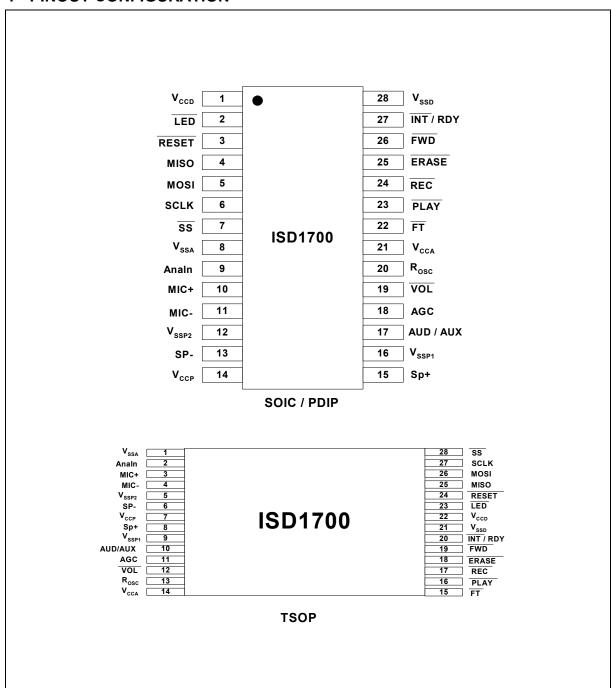

# **4 PINOUT CONFIGURATION**

# **5 PIN DESCRIPTION**

| PIN<br>NAME      | PDIP /<br>SOIC | TSOP | FUNCTIONS [3]                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CCD</sub> | 1              | 22   | <b>Digital Power Supply</b> : It is important to have a separate path for each power signal including $V_{\text{CCD}}$ , $V_{\text{CCA}}$ and $V_{\text{CCP}}$ to minimize the noise coupling. Decoupling capacitors should be as close to the device as possible.                                                                                                                                                          |

| LED              | 2              | 23   | <b>LED</b> : With an LED connected, this output turns an LED on during recording and blinks LED during playback, forward and erase operations.                                                                                                                                                                                                                                                                              |

| RESET            | 3              | 24   | <b>RESET</b> : When Low, the device enters into a known state and initializes all pointers to the default state. This pin has an internal pull-up resistor [1].                                                                                                                                                                                                                                                             |

| MISO             | 4              | 25   | <b>Master In Slave Out:</b> Data is shifted out on the falling edge of SCLK. When the SPI is inactive ( $\overline{SS}$ = high), it's tri-state.                                                                                                                                                                                                                                                                            |

| MOSI             | 5              | 26   | <b>Master Out Slave In:</b> Data input of the SPI interface when the device is configured as slave. Data is latched into the device on the rising edge of SCLK. This pin has an internal pull-up resistor <sup>[1]</sup> .                                                                                                                                                                                                  |

| SCLK             | 6              | 27   | <b>Serial Clock</b> : Clock of the SPI interface. It is usually generated by the master device (typically microcontroller) and is used to synchronize the data transfer in and out of the device through the MOSI and MISO lines, respectively. This pin has an internal pull-up resistor <sup>[1]</sup> .                                                                                                                  |

| SS               | 7              | 28   | <b>Slave Select:</b> This input, when low, selects the device as slave device and enables the SPI interface. This pin has an internal pull-up resistor [1].                                                                                                                                                                                                                                                                 |

| $V_{SSA}$        | 8              | 1    | <b>Analog Ground</b> : It is important to have a separate path for each ground signal including $V_{SSA}$ , $V_{SSD}$ , $V_{SSP1}$ and $V_{SSP2}$ to minimize the noise coupling.                                                                                                                                                                                                                                           |

| Analn            | 9              | 2    | Analn: Auxiliary analog input to the device for recording or feed-through. An AC-coupling capacitor (typical 0.1uF) is necessary and the amplitude of the input signal must not exceed 1.0 Vpp. Depending upon the D3 of APC register, Analn signal can be directly recorded into the memory, mixed with the Mic signal then recorded into the memory or buffered to the speaker and AUD/AUX outputs via feed-through path. |

| MIC+             | 10             | 3    | <b>MIC+:</b> Non-inverting input of the differential microphone signal. The input signal should be AC-coupled to this pin via a series capacitor. The capacitor value, together with an internal 10 $\rm K\Omega$ resistance on this pin, determines the low-frequency cutoff for the pass band filter. The Mic analog path is also controlled by D4 of APC register.                                                       |

| MIC-             | 11             | 4    | <b>MIC-</b> : Inverting input of the differential microphone signal. The input signal should be AC-coupled to the MIC+ pin. It provides input noise-cancellation, or common-mode rejection, when the microphone is connected differentially to the device. The Mic analog path is also controlled by D4 of APC register.                                                                                                    |

| $V_{\rm SSP2}$   | 12             | 5    | <b>Ground for Negative PWM Speaker Driver</b> : It is important to have a separate path for each ground signal including $V_{SSA}$ , $V_{SSD}$ , $V_{SSP1}$ and $V_{SSP2}$ to minimize the noise coupling.                                                                                                                                                                                                                  |

| PIN<br>NAME       | PDIP /<br>SOIC | TSOP | FUNCTIONS [3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SP-               | 13             | 6    | <b>SP-</b> : The negative Class D PWM provides a differential output with SP+ pin to directly drive an 8 $\Omega$ speaker or typical buzzer. During power down or not used, this pin is tri-stated. This output can be controlled by D8 of APC register. The factory default is set at on state.                                                                                                                                                                                                                                                                                                                                      |

| V <sub>CCP</sub>  | 14             | 7    | <b>Power Supply for PWM Speaker Driver</b> : It is important to have a separate path for each power signal including $V_{\text{CCD}}$ , $V_{\text{CCA}}$ and $V_{\text{CCP}}$ to minimize the noise coupling. Decoupling capacitors to $V_{\text{SSP1}}$ and $V_{\text{SSP2}}$ should be as close to the device as possible. The $V_{\text{CCP}}$ supply and $V_{\text{SSP}}$ ground pins have large transient currents and need low impedance returns to the system supply and ground, respectively.                                                                                                                                 |

| SP+               | 15             | 8    | <b>SP+:</b> The positive Class D PWM provides a differential output with the SP- pin to directly drive an 8 $\Omega$ speaker or typical buzzer. During power down or not used, this pin is tri-stated. This output can be controlled by D8 of APC register. The factory default is set at on state.                                                                                                                                                                                                                                                                                                                                   |

| V <sub>SSP1</sub> | 16             | 9    | <b>Ground for Positive PWM Speaker Driver</b> : It is important to have a separate path for each ground signal including $V_{SSA}$ , $V_{SSD}$ , $V_{SSP1}$ and $V_{SSP2}$ to minimize the noise coupling.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| AUD /<br>AUX      | 17             | 10   | Auxiliary Output: Depending upon the D7 of APC register, this output is either an AUD or AUX output. AUD is a single-ended current output, whereas AUX is a single-ended voltage output. They can be used to drive an external amplifier. The factory default is set to AUD. This output can be powered down by D9 of APC register. The factory default is set to On state. For AUD output, there is a ramp up at beginning and ramp down at the end to reduce the pop.                                                                                                                                                               |

| AGC               | 18             | 11   | <b>Automatic Gain Control (AGC)</b> : The AGC adjusts the gain of the preamplifier dynamically to compensate for the wide range of microphone input levels. The AGC allows the full range of signals to be recorded with minimal distortion. The AGC is designed to operate with a nominal capacitor of 4.7 $\mu$ F connected to this pin.  Connecting this pin to ground (V <sub>SSA</sub> ) provides maximum gain to the preamplifier circuitry. Conversely, connecting this pin to the power supply (V <sub>CCA</sub> ) provides minimum gain to the preamplifier circuitry.                                                       |

| VOL               | 19             | 12   | <b>Volume:</b> This control has 8 levels of volume adjustment. Each Low going pulse decreases the volume by one level. Repeated pulses decrease volume level from current setting to minimum then increase back to maximum, and continue this pattern. During power-up or $\overline{RESET}$ , a default setting is loaded from non-volatile configuration. The factory default is set to maximum. This output can also be controlled by <d2:d0> of APC register. This pin has an internal pull-up device [1] and an internal debounce <math>(T_{Deb})</math> [2] for start and end allowing the use of a push button switch.</d2:d0> |

| R <sub>osc</sub>  | 20             | 13   | <b>Oscillator Resistor</b> : A resistor connected from R <sub>OSC</sub> pin to ground determines the sample frequency of the device, which sets the duration. Please refer to the Duration Section for details.                                                                                                                                                                                                                                                                                                                                                                                                                       |

October 2006 - 11 - Revision 0

| <b>-</b>         |                |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN<br>NAME      | PDIP /<br>SOIC | TSOP | FUNCTIONS [3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>CCA</sub> | 21             | 14   | <b>Analog Power Supply</b> . It is important to have a separate path for each power signal including $V_{\text{CCD}}$ , $V_{\text{CCA}}$ and $V_{\text{CCP}}$ to minimize the noise coupling. Decoupling capacitors to $V_{\text{SSA}}$ should be as close to the device as possible.                                                                                                                                                                                                                                                |

| FT               | 22             | 15   | <b>Feed-through:</b> In Standalone mode, when FT is engaged low, the Analn feed-through path is activated. As a result, the Analn signal is transmitted directly from Analn to both Speaker and AUD/AUX outputs with Volume Control. However, SPI overrides this input, while in SPI mode, and feed-through path is controlled by a D6 of APC register. This pin has an internal pull-up device [1] and an internal debounce (T <sub>Deb</sub> ) [2] for start and end allowing the use of a push button switch.                     |

| PLAY             | 23             | 16   | <b>Playback:</b> Pulsing <b>PLAY</b> to Low once initiates a playback operation. Playback stops automatically when it reaches the end of the message. Pulsing it to Low again during playback stops the operation.                                                                                                                                                                                                                                                                                                                   |

|                  |                |      | Holding <b>PLAY</b> Low constantly functions as a sequential playback operation loop. This looping continues until <b>PLAY</b> returns to High. This pin has an internal pull-up device <sup>[1]</sup> and an internal debounce (T <sub>Deb</sub> ) <sup>[2]</sup> for start and end allowing the use of a push button switch.                                                                                                                                                                                                       |

| REC              | 24             | 17   | <b>Record:</b> The device starts recording whenever $\overline{\text{REC}}$ switches from High to Low and stays at Low. Recording stops when the signal returns to High. This pin has an internal pull-up device [1] and an internal debounce $(T_{Deb})^{[2]}$ for start allowing the use of a push button switch.                                                                                                                                                                                                                  |

| ERASE            | 25             | 18   | <b>Erase:</b> When active, it starts an erase operation. Erase operation will take place only when the playback pointer is positioned at either the first or last message. Pulsing this pin to Low enables erase operation and deletes the current message. Holding this pin Low for more than 3 sec. initiates a global erase operation, and will delete all the messages. This pin has an internal pull-up device [1] and an internal debounce (T <sub>Deb</sub> ) [2] for start and end allowing the use of a push button switch. |

| FWD              | 26             | 19   | <b>Forward:</b> When triggered, it advances to the next message from the current location, when the device is in power down status. During playback cycle, pulsing this pin Low stops the current playback operation and advances to the next message, and then re-starts the playback operation of the new message. This pin has an internal pull-up device and an internal debounce $(T_{Deb})^{[2]}$ for start and end allowing the use of a push button switch.                                                                  |

| RDY/INT          | 27             | 20   | An open drain output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                  |                |      | Ready (Standalone mode): This pin stays Low during record, play, erase and forward operations and stays High in power down state                                                                                                                                                                                                                                                                                                                                                                                                     |

|                  |                |      | Interrupt (SPI mode):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                  |                |      | After completing the SPI command, an active low interrupt is generated. Once the interrupt is cleared, it returns to High.                                                                                                                                                                                                                                                                                                                                                                                                           |

October 2006 - 12 - Revision 0

| PIN<br>NAME      | PDIP /<br>SOIC | TSOP | FUNCTIONS [3]                                                                                                                                                                                  |  |  |  |  |  |  |

|------------------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| V <sub>SSD</sub> | 28             | 21   | <b>Digital Ground</b> : It is important to have a separate path for each ground signal including $V_{\rm SSA},\ V_{\rm SSD},\ V_{\rm SSP1}$ and $V_{\rm SSP2}$ to minimize the noise coupling. |  |  |  |  |  |  |

October 2006 - 13 -Revision 0

Note:  $^{[1]}$  600 k $\Omega$   $^{[2]}$  TDeb = Refer to AC Timing  $^{[3]}$  For any unused pins, left floated.

#### **6 FUNCTIONAL DESCRIPTION**

#### 6.1 DETAILED DESCRIPTION

#### 6.1.1 Audio Quality

Winbond's patented ChipCorder<sup>®</sup> Multi-Level Storage (MLS) technology provides a natural, high-quality record and playback solution on a single chip. The input voice signals are stored directly in the Flash memory and are reproduced in their natural form without any of the compression artifacts caused by digital speech solutions.

## 6.1.2 Message Duration

The ISD1700 Series offer record and playback duration from 20 seconds to 480 seconds. Sampling frequency and message duration,  $T_{Dur}$ , are determined by an external resistor connected to the  $R_{OSC}$  pin.

Table 6.1 Duration vs. Sampling Frequency

| Sample Freq. | ISD1730 | ISD1740 | ISD1750  | ISD1760  | ISD1790  | ISD17120 | ISD17150 | ISD17180 | ISD17210 | ISD17240 |

|--------------|---------|---------|----------|----------|----------|----------|----------|----------|----------|----------|

| 12 kHz       | 20 secs | 26 secs | 33 secs  | 40 secs  | 60 secs  | 80 secs  | 100 secs | 120 secs | 140 secs | 160 secs |

| 8 kHz        | 30 secs | 40 secs | 50 secs  | 60 secs  | 90 secs  | 120 secs | 150 secs | 180 secs | 210 secs | 240 secs |

| 6.4 kHz      | 37 secs | 50 secs | 62 secs  | 75 secs  | 112 secs | 150 secs | 187 secs | 225 secs | 262 secs | 300 secs |

| 5.3 kHz      | 45 secs | 60 secs | 75 secs  | 90 secs  | 135 secs | 181 secs | 226 secs | 271 secs | 317 secs | 362 secs |

| 4 kHz        | 60 secs | 80 secs | 100 secs | 120 secs | 180 secs | 240 secs | 300 secs | 360 secs | 420 secs | 480 secs |

#### 6.1.3 Flash Storage

The ISD1700 devices utilize embedded Flash memory to provide non-volatile storage. A message can be retained for a minimum of 100 years without power. Additionally, each device can be re-recorded over 100,000 times (typical).

#### 6.2 MEMORY ARRAY ARCHITECTURE

The memory array provides storage of four special Sound Effects (SEs) as well as the voice data. The memory array is addressed by rows. A row is the minimum storage resolution by which the memory can be addressed. The memory assignment is automatically handled by the internal message management system in standalone mode. While in SPI mode, one has the full access to the entire memory via the eleven address bits. Table 6.2 shows the minimum storage resolution with respect to the sampling frequency.

Table 6.2 Minimum Storage Resolution vs. Sampling Frequency

| Sampling Frequency         | 12 kHz    | 8 kHz    | 6.4 kHz  | 5.3 kHz  | 4 kHz    |

|----------------------------|-----------|----------|----------|----------|----------|

| Minimum Storage Resolution | 83.3 msec | 125 msec | 156 msec | 187 msec | 250 msec |

For example, at 8 kHz sampling frequency, the minimum storage resolution is 125 msec, so each Sound Effect (SE) is approximately 0.5 second long.

October 2006 - 14 - Revision 0

Table 6.3 shows the maximum row address of each device in the ISD1700 family. The four sound effects (SE) occupy the first sixteen rows in the memory array with four rows for each SE. That means from address 0x000 to address 0x00F. The remaining memory is dedicated to voice data storage. Hence, the address of voice message storage will start from 0x010 to the end of memory array.

**Table 6.3 Device Maximum Row Address**

| ı | Device             | ISD1730 | ISD1740 | ISD1750 | ISD1760 | ISD1790 | ISD17120 | ISD17150 | ISD17180 | ISD17210 | ISD17240 |

|---|--------------------|---------|---------|---------|---------|---------|----------|----------|----------|----------|----------|

|   | Maximum<br>Address | 0x0FF   | 0x14F   | 0x19F   | 0x1EF   | 0x2DF   | 0x3CF    | 0x4BF    | 0x5AF    | 0x69F    | 0x78F    |

Below figure shows the memory array architecture for ISD1700 series.

| •         | • •                      |  |

|-----------|--------------------------|--|

| 000 - 003 | SE1                      |  |

| 004 - 007 | SE2                      |  |

| 008 - 00B | SE3                      |  |

| 00C - 00F | SE4                      |  |

| 010       | 1st row of Voice Message |  |

|           |                          |  |

| 0FF       | Last row of ISD1730      |  |

| 14F       | Last row of ISD1740      |  |

| 19F       | Last row of ISD1750      |  |

| 1EF       | Last row of ISD1760      |  |

|           |                          |  |

| 2DF       | Last row of ISD1790      |  |

|           |                          |  |

|           |                          |  |

| 3CF       | Last row of ISD17120     |  |

|           |                          |  |

| 4BF       | Last row of ISD17150     |  |

| 131       | 2400 1011 01 102 11 100  |  |

|           |                          |  |

| 5AF       | Last row of ISD17180     |  |

|           |                          |  |

| 69F       | Last row of ISD17190     |  |

| 095       | Last row of ISD17180     |  |

|           |                          |  |

| 78F       | Last row of ISD17240     |  |

|           |                          |  |

Accessible by SPI Set Commands or SE mode

Accessible by

SPI Set Commands

or

Standalone Alike SPI Commands

#### 6.3 MODES OF OPERATIONS

The ISD1700 Series can operate in either Standalone (Push-Button) or microcontroller (SPI) mode.

#### 6.3.1 Standalone (Push-Button) Mode

Standalone operation entails use of the REC, PLAY, FT, FWD, ERASE, VOL and RESET pins to trigger operations. The internal state machine automatically configures the audio path according to the desired operation. In this mode, the internal state machine takes full control on message management. This allows the user to record, playback, erase, and forward messages without the needs to know the exact addresses of the messages stored inside the memory. For additional information, refer to Standalone Mode Design Reference Guide.

#### 6.3.2 SPI Mode

In SPI mode, control of the device is achieved through the 4-wire serial interface. Commands similar to the push button controls, such as  $\overline{\text{REC}}$ ,  $\overline{\text{PLAY}}$ ,  $\overline{\text{FT}}$ ,  $\overline{\text{FWD}}$ ,  $\overline{\text{ERASE}}$ ,  $\overline{\text{VOL}}$  and  $\overline{\text{RESET}}$ , can be executed through the SPI interface. In addition, there are commands that allow the modification of the analog path configuration, as well as commands that direct access the memory address of the array, plus others. The SPI mode allows full control of the device and the ability to perform complex message management rather than conform to the circular memory architecture as push-button mode. Refer to SPI Mode sections for details.

In addition, it is suggested that both the microcontroller and the ISD1700 device have the same power supply level for design simplicity.

In either mode, it is strongly recommended that any unused pins, no matter input or output, must be left floated or unconnected. Otherwise, it will cause the device becoming malfunction.

October 2006 - 16 - Revision 0

# 7 ANALOG PATH CONFIGURATION (APC)

The analog path of the ISD1700 can be configured to accommodate a wide variety of signal path possibilities. This includes the source of recording signals, mixing of input signals, mixing the playback signal with an input signal to the outputs, feed-through signal to the outputs and which outputs being activated.

The active analog path configuration is determined by a combination of the internal state of the device, i.e. desired operation (record or playback), the status of the  $\overline{FT}$  and the contents of the APC register. The APC register is initialized by the internal non-volatile configuration (NVCFG) bits upon power-on-reset or reset function. The APC register can be read and loaded using SPI commands.

The factory default of NVCFG bits, <D11:D0>, is 0100 0100 0000 = 0x440. This configures the device with recording through the MIC inputs, FT via Analn input, playback from MLS, SE editing feature enabled, maximum volume level, active PWM driver and AUD current outputs. One can use SPI commands to modify the APC register and store it permanently into the NVCFG bits.

#### 7.1 APC REGISTER

Details of the APC register are shown in Table 7.1.

**Table 7.1 APC Register**

| Bit | Name          |            | D                                 | escription                                                     | Default              |

|-----|---------------|------------|-----------------------------------|----------------------------------------------------------------|----------------------|

| D0  | VOL0          |            |                                   | 2:D0>: These provide 8 steps of                                | 000 (maximum)        |

| D1  | VOL1          |            |                                   | adjustment. Each bit changes ep, where 000 = maximum and       |                      |

| D2  | VOL2          | 111 = mir  |                                   | sp, where ood maximum and                                      |                      |

| D3  | Monitor_Input | Monitor in | nput signal at                    | outputs during recording.                                      | 0 = Monitor_input is |

|     |               | D3 = 0     | Disable inpu                      | t signal to outputs during record                              | Disabled             |

|     |               | D3 = 1     | Enable inpu                       | t signal to outputs during record                              |                      |

| D4  | Mix_Input     |            | PI mode, D4                       | standalone mode or SPI_FT bit controls the input selection for | 0 = Mix_Input is Off |

|     |               | D4 = 0     | <del>FT</del> / D6= 0             | Analn REC                                                      |                      |

|     |               |            | FT / D6= 1                        | Mic REC                                                        |                      |

|     |               | D4 = 1     | FT / D6= 0                        | (Mic + Analn) REC                                              |                      |

|     |               |            | <del>FT</del> / D6= 1             |                                                                |                      |

| D5  | SE_Editing    |            | r disable editir<br>nere 0 = Enab | 0 = Enable<br>SE_Editing                                       |                      |

October 2006 - 17 - Revision 0

| Bit | Name                      |                            | Description                                                                                                                                                                                                  | Default           |

|-----|---------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| D6  | SPI_FT                    | the FT (D6) with through t | mode only. Once SPI_PU command is sent, is disabled and replaced by this control bit the same functionality. After exiting SPI mode he PD command, the $\overline{FT}$ resumes control of ugh (FT) function. | 1 = SPI_FT is Off |

|     |                           | D6 = 0                     | FT function in SPI mode is On                                                                                                                                                                                |                   |

|     |                           | D6 = 1                     | FT function in SPI mode is Off                                                                                                                                                                               |                   |

| D7  | Analog Output:<br>AUD/AUX | Select Al                  | JD or AUX: 0 = AUD, 1 = AUX                                                                                                                                                                                  | 0 = AUD           |

| D8  | PWM SPK                   | PWM Sp                     | eaker +/- outputs: 0 = Enabled, 1 = Disabled                                                                                                                                                                 | 0 = PWM enabled   |

| D9  | PU Analog<br>Output       | PowerUp                    | analog output: 0 = On, 1 = Off                                                                                                                                                                               | 0 = On            |

| D10 | vAlert                    | vAlert: 0                  | = On, 1 = Off.                                                                                                                                                                                               | 1 = Off           |

| D11 | EOM Enable                | When thi                   | able for SetPlay operation: 0 = Off, 1 = On. s bit is set to 1, SetPlay operation will stop at ation, rather than the End Address.                                                                           | 0 = Off           |

#### 7.2 DEVICE ANALOG PATH CONFIGURATIONS

Table 7.2 demonstrates the possible analog path configurations with ISD1700. The device can be in power-down, power-up, recording, playback and/or feed-through state depending upon the operation requested by the push-buttons or related SPI commands. The active path in each of these states is determined by D3 and D4 of the APC register, as well as either D6 of the APC register in SPI mode or the  $\overline{\text{FT}}$  status in standalone mode. In addition,.D7~D9 of the APC register determine which output drivers are activated.

**Table 7.2 Operational Paths**

| APC   | Regist    | er        | Operational Paths |                                         |                    |  |

|-------|-----------|-----------|-------------------|-----------------------------------------|--------------------|--|

| D6/FT | D4<br>Mix | D3<br>Mon | ldle              | Record                                  | Playback           |  |

| 0     | 0         | 0         | Analn FT          | Analn Rec                               | (Analn + MLS)> o/p |  |

| 0     | 0         | 1         | Analn FT          | Analn Rec + Analn FT                    | (Analn + MLS)> o/p |  |

| 0     | 1         | 0         | (Mic + Analn) FT  | (Mic + Analn) Rec                       | (Analn + MLS)> o/p |  |

| 0     | 1         | 1         | (Mic + Analn) FT  | (Mic + Analn) Rec +<br>(Mic + Analn) FT | (Analn + MLS)> o/p |  |

| 1     | 0         | 0         | FT Disable        | Mic Rec                                 | MLS> o/p           |  |

| 1     | 0         | 1         | FT disable        | Mic Rec + Mic FT                        | MLS> o/p           |  |

| 1     | 1         | 0         | FT disable        | Mic Rec                                 | MLS> o/p           |  |

| 1     | 1         | 1         | FT disable        | Mic Rec + Mic FT                        | MLS> o/p           |  |

October 2006 - 18 - Revision 0

## 8 STANDALONE (PUSH-BUTTON) OPERATIONS

One can utilize the REC, PLAY, FT, FWD, ERASE, VOL or RESET control to initiate a desired operation. As completed, the device automatically enters into the power-down state. An unique message management system is executed under this mode, which links to an optional special Sound Effect (SE) feature to review certain operating status of the device. Hence, it is benefit to understand how SE functions first.

#### 8.1 SOUND EFFECT (SE) MODE

SE mode can be manipulated by several control pins as described below. There are four special sound effects (SE1, SE2, SE3, and SE4). Audio clips can be programmed into the SEs as various indications. Each SE occupies four designated memory rows and the first sixteen memory rows are reserved for these four SEs evenly and sequentially.

#### 8.1.1 Sound Effect (SE) Features

The functions of SEs are used to indicate the status of the following operations:

- SE1: Beginning of recording, forward or global erase warning

- SE2: End of recording, single erase or forward from last message

- SE3: Invalid erase operation

- SE4: Successful global erase

In general, the LED flashes once for SE1, twice for SE2, and so forth. It is crucial to recognize that the LED flashes accordingly regardless the SEs are programmed or not. When none of them is programmed, the blinking periods of SE1, SE2, SE3 and SE4 are defined as  $T_{LS1}$ ,  $T_{LS2}$ ,  $T_{LS3}$  and  $T_{LS4}$ , respectively. Once they are programmed, during operation, the device flashes LED and plays the related SE simultaneously. Nevertheless, the period of blinking LED, under this condition, is limited by the duration of the recorded SE. In addition, they are defined as  $T_{SE1}$ ,  $T_{SE2}$ ,  $T_{SE3}$  and  $T_{SE4}$ , respectively. These timing parameters also apply to the conditions elaborated in the following related sections. (Refer to AC timing parameter for details.)

## 8.1.2 Entering SE Mode

- First press and hold FWD Low for 3 seconds or more roughly. This action on FWD will usually blink LED once (and play SE1 simultaneously if SE1 is recorded). However, if playback pointer is at the last message or memory is empty, the chip will blink the LED twice (and play SE2 simultaneously if SE2 is recorded).

- While holding FWD Low, press and hold the REC Low until the LED blinks once.

- The LED flashing once again indicates that the device is now in SE mode. Once entering

into SE mode, the SE1 is always the first one to be accessible.

#### 8.1.3 SE Editing

After into SE editing mode, one can perform record, play, or erase operation on each SE by pressing the appropriate buttons. For example, to record SE, simply press and hold

October 2006 - 19 - Revision 0

**REC**. Similarly for play or erase function, pulse **PLAY** or **ERASE**, respectively. Record source can be either Mic+/- or Analn.

- A subsequent FWD operation moves the record and playback pointers to the next SE sequentially. The LED will also blink one to four times after such operation to indicate which SE is active. If FWD is pressed while in SE4, the LED will flash once to indicate that SE1 is again active.

- While the LED is blinking, the device will ignore any input commands. One must wait

patiently until the LED stops blinking completely before any record, play, erase or

forward input should be sent.

#### 8.1.4 Exiting SE Mode

• The required steps are the same as Entering SE mode. First press and hold **FWD** until the LED stops blinking (and related SE is played if SEs are programmed). Then, simultaneously press and hold the **REC** Low until the LED blinks twice (and device will play SE2 if SE2 is programmed). The device now exits the SE editing mode.

#### 8.1.5 Sound Effect Duration

The duration of SEs is determined by the sampling frequency selected and illustrated in below table.

Table 8.1 Sound Effect Duration vs. Sampling Frequency

| Sampling Frequency | 12 kHz   | 8 kHz   | 6.4 kHz   | 5.3 kHz  | 4 kHz |

|--------------------|----------|---------|-----------|----------|-------|

| Duration of SE     | 0.33 sec | 0.5 sec | 0.625 sec | 0.75 sec | 1 sec |

#### 8.2 OPERATION OVERVIEW

After power is applied or power-on-reset (POR), the device is in the factory default state and two internal record and playback pointers are initialized. (These two pointers are discussed later.) Then the active analog path is determined by the state of the  $\overline{\text{FT}}$ , the status of the APC register and the desired operation.

Up to four optional sound effects (SE1~SE4) can be programmed into the device to provide audible feedback to alert the user about the operating status. Simultaneously, the LED output provides visual indication about the operating status. During the active state of LED output, no new command will be accepted.

An unique message management technique is implemented. Under this mode, the recorded messages are stored sequentially into the embedded memory from the beginning to the end in a circular fashion automatically.

Two internal pointers, the record pointer and playback pointer, determine the location where an operation starts. After POR, these pointers are initialized as follows:

If no messages are present, both point to the beginning of memory.

October 2006 - 20 - Revision 0

If messages are present, the record pointer points to the next available memory row following the last message and the playback pointer points to the beginning of the last recorded message.

The playback pointer is affected either by the FWD or REC operation. The record pointer is updated to the next available memory row after each REC operation.

#### 8.2.1 Record Operation

The  $\overline{REC}$  controls recording operation. Once setting this pin Low, the device starts recording from the next available row in memory and continues recording until either the  $\overline{REC}$  returns to High or the memory is full. The source of recording is from either MIC+/- or AnaIn, whereas the active analog configuration path is determined by the desired operation and the state of the  $\overline{FT}$ . The  $\overline{REC}$  is debounced internally. After recording, the record pointer will move to the next available row from the last recorded message and the playback pointer will position at the beginning of the newly recorded message.

However, it is important to perform an Erase operation on the desired location before any recording proceeds. In addition, the power supply must remain On during the entire recording process. If power is interrupted during recording process, the circular memory architecture will be destroyed. As a result, next time when a push button operation starts, the LED will blink seven times, which indicates that something unusual has occurred, and the device will fail to perform the requested operation. Under such scenario, the only way to recover the chip to a proper state is to perform a Global Erase operation.

#### Message recording indicators:

The built-in message management technique associates special Sound Effects, SE1 and SE2, within the recording process.

- a) When REC goes Low:

- If SE1 is not programmed, then the LED turns On immediately to indicate that a recording is in progress.

- If SE1 is programmed, device plays SE1 and blinks LED simultaneously. Then LED turns On to show recording is in process. The LED blinking period of SE1 is determined by the recorded duration of SE1 (T<sub>SE1</sub>). (Refer to AC timing parameter and timing diagrams for details.)

- b) When **REC** goes High or when the memory is full:

- If SE2 is not programmed, then the LED turns Off immediately to indicate that the recording halts.

- If SE2 is programmed, device plays SE2 and flashes LED simultaneously. Then LED turns Off to show recording stops. The LED blinking period of SE2 is determined by the recorded duration of SE2 (T<sub>SE2</sub>).

Triggering of **REC** during a play, erase or forward operation is an illegal operation and will be ignored.

October 2006 - 21 - Revision 0

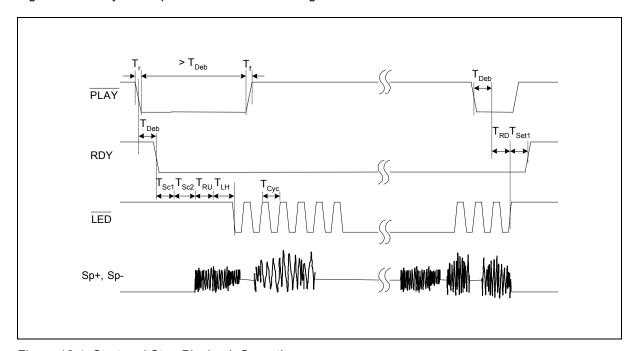

#### 8.2.2 Playback Operation

Two playback modes can be executed by **PLAY**, which is internally debounced.

- a) *Edge-trigger mode*: Pulsing PLAY Low once initiates a playback operation of the current message. Playback automatically stops at the end of the message. Pulsing PLAY again will re-play the message. During playback, the LED flashes and goes Off when the playback completes. Pulsing PLAY to Low again during playback stops the playback operation. Under these circumstances, the playback pointer remains at the start of the played message after the operation is completed.

- b) **Looping Playback mode**: As  $\overline{\text{PLAY}}$  is held Low constantly, the device plays all messages sequentially from the current message to its previous message and loops the playback action. During the entire playback process, the LED flashes non-stop. Meanwhile, the looping playback mechanism is implemented in the following sequence: start playback from current message; as playback is over, perform a forward operation; start playback of new message; once playback completes, perform another forward action; start playback of new message, .....and so on. This looping pattern continues until  $\overline{\text{PLAY}}$  is released. As  $\overline{\text{PLAY}}$  is released, device will continue to playback the current message until completion. When playback stops, the playback pointer is set at the start of the halted message.

If no SE1 and SE2 are programmed, after playing a message, except the last one, device flashes LED once with blinking period  $T_{LS1}$  due to forward action. As after the last message, device flashes LED twice with blinking period  $T_{LS2}$ .

If both SE1 and SE2 are programmed, after playing a message, except the last one, device plays SE1 and flashes LED simultaneously due to forward action. Then device keeps on the playback of new message. Alternatively, after playing the last message, device plays SE2 and flashes LED simultaneously due to forward action. Then device maintains the playback of the first message. The LED blinking period of SE1 and SE2 are determined by the recorded durations of SE1 and SE2, respectively.

Triggering **PLAY** during a record, erase, or forward operation is an illegal operation and will be ignored.

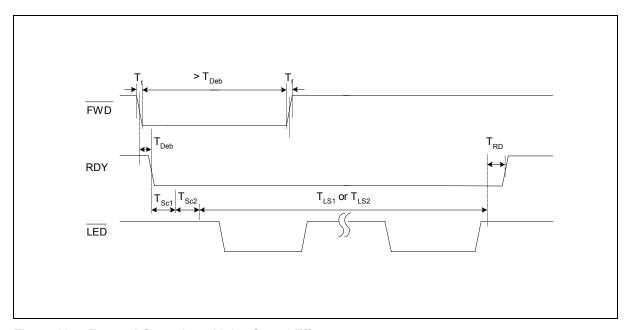

#### 8.2.3 Forward Operation

The  $\overline{FWD}$  allows the device to advance the playback pointer to the next message in a forward direction. When the pointer reaches the last message, it will jump back to the first message. Hence, the movement is alike a circular fashion among the messages. The  $\overline{FWD}$  is debounced internally. The effect of a Low-going pulse on the  $\overline{FWD}$  depends on the current state of the device:

- a) If the device is in power-down state and the playback pointer does not point to the last message, then:

- The playback pointer will advance to the next message.

- If SE1 is not recorded, device will flash LED once with blinking period T<sub>LS1</sub>.

- However, if SE1 is recorded, device plays SE1 and blinks the LED once simultaneously. The LED blinking period is determined by the recorded duration, T<sub>SE1</sub>, of SE1.

October 2006 - 22 - Revision 0

- b) If the device is in power-down state and the playback pointer points to the last message, then:

- The playback pointer will advance to the first message.

- If SE2 is not recorded, device will flash LED twice with blinking period T<sub>LS2</sub>.

- ullet However, if SE2 is recorded, device plays SE2 and blinks the LED twice simultaneously. The LED blinking period is determined by the recorded duration,  $T_{\text{SE2}}$ , of SE2.

- c) If the device is currently playing a message that is not the last one, then the device:

- Halts the playback operation.

- · Advances the playback pointer to the next message.

- If SE1 is not recorded, device will flash LED once with blinking period T<sub>LS1</sub>.

- However, if SE1 is recorded, device plays SE1 and blinks the LED once simultaneously. The LED blinking period is determined by the recorded duration, T<sub>SE1</sub>, of SE1.

- Playback the new message.

- The LED flashes during this entire process.

- d) If the device is currently playing the last message, then the device:

- Halts the playback operation.

- Advances the playback pointer to the first message.

- If SE2 is not recorded, device will flash LED twice with blinking period T<sub>182</sub>.

- However, if SE2 is recorded, device simultaneously plays SE2 and blinks the LED twice. The LED blinking period is determined by the recorded duration,  $T_{\text{SE2}}$ , of SE2.

- · Playback the first message.

- The LED flashes during this entire process.

Triggering of the **FWD** operation during an erase or record operation is an illegal operation and will be ignored.

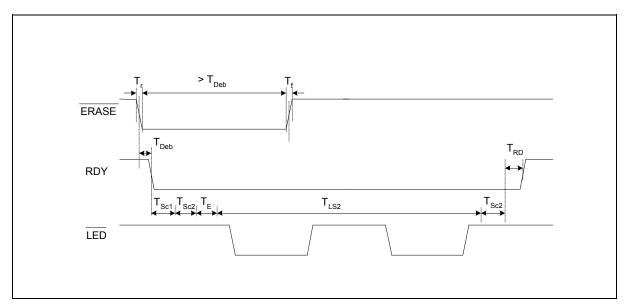

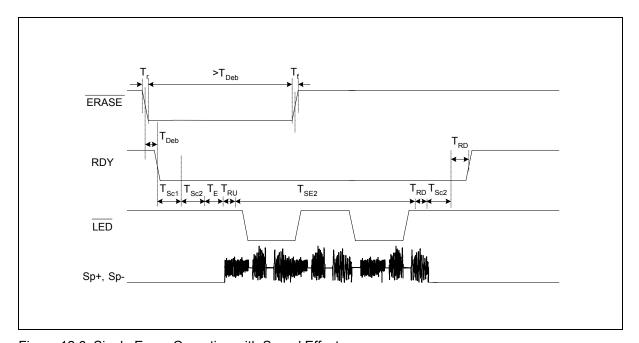

#### 8.2.4 Erase Operation

Erasing individual message takes place only if the playback pointer is at either the first or the last message. Erasing individual messages other than the first or last message is not permitted in standalone mode. However, global erase can be executed at any message location and will erase all messages, once completed successfully. The **ERASE** is debounced internally. These two erase modes are described as follows:

- a) Individual Erase: Only the first or last messages can be individually erased. Pulsing ERASE Low enables device responses differently pending upon the status of the device and the current location of the playback pointer:

- If the device is in power down mode and the playback pointer currently points to the first (or last) message, then the device will:

October 2006 - 23 - Revision 0

- Erase first (or last) message and flash LED twice with blinking period T<sub>LS2</sub>, if SE2 is not programmed.

- o If SE2 is programmed, simultaneously play SE2 and flash the LED twice. The LED blinking period is determined by the recorded duration, T<sub>SE2</sub>, of SE2.

- Update the playback pointer to the new first message previously the second message (or new last message - originally the second to the last message).

- If the device is in power down mode and the playback pointer is at any message other than the first or last message, then the device will:

- Not erase any message and flash LED three times with blinking period T<sub>LS3</sub>, if SE3 is not programmed.

- o If SE3 is programmed, simultaneously play SE3 and flash the LED three times. The LED blinking period is determined by the recorded duration, T<sub>SE3</sub>, of SE3.

- Not change to the playback pointer.

- If the device is currently playing the first (or last) message,

- Stops the playback operation.

- Erases the message as scenario one of individual erase mentioned earlier.

- If the device is currently playing any message other than the first or last message, then

the device will:

- Stops the playback operation.

- o Behave like scenario two of individual erase mentioned above.

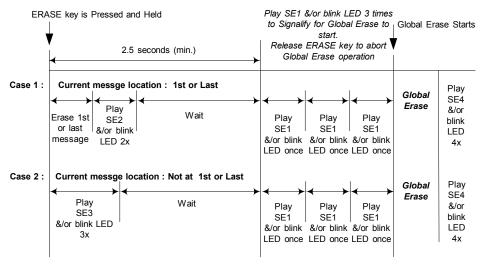

- b) **Global Erase**: Level-triggering **ERASE** at Low for more than 2.5 seconds and holding it continuously will initiate the Global Erase operation and deletes all messages, except the Sound Effects (SEs). See the below figure for operation details. The device reacts differently according to the current condition of the device.

- If SEs are not programmed

- The device will blink LED twice with blinking period T<sub>LS2</sub> once **ERASE** is triggered to indicate the current message being erased if it is either the first or last one.

- Or if current message is neither the first nor last one, LED will blink three times with blinking period  $T_{LS3}$  to show that current message is not erased.

- o If **ERASE** is kept Low constantly, the LED will be blinked seven times to indicate all messages being erased. However, if **ERASE** is released before the first three blinks of LED, then global erase operation will be abandoned. Otherwise, the global erase operation will be performed. The estimated total period of blinking seven times is defined as (3\*T<sub>LS1</sub>+T<sub>LS4</sub>).

- If SEs are programmed,

- The device will play SE2 and flash the LED twice simultaneously once ERASE is triggered to indicate the current message being erased if it is either the first or last one.

- Or if current message is neither the first nor last one, the device will play SE3 and flash the LED three times simultaneously to indicate that current message is not erased.

October 2006 - 24 - Revision 0

- After **ERASE** continues to be held Low for 2.5 seconds or more, the device plays SE1 three times with LED flashing simultaneously. This serves as a warning signal that after playing SE1 three times, then global erase will be performed. However, if **ERASE** is released before the playback of the third SE1, then global erase operation will be abandoned.

- As ERASE is maintained Low continuously, the device will erase all messages and play SE4 with LED flashing simultaneously upon completion.

- Ouring this process, the blinking periods of twice, three times and four times are limited by the recorded durations of SE2, SE3 and SE4 ( $T_{SE2}$ ,  $T_{SE3}$  and  $T_{SE4}$ ) respectively.

However, it is vital to maintain the power supply On during the erase process. If power is interrupted during such process, the circular memory architecture will be destroyed. As a result, next time when a push button operation starts, the LED will blink seven times, which indicates that something abnormal has occurred, and the device will fail to perform the requested operation. Under such scenario, the only way to recover the chip to a proper state is to perform a Global Erase operation.

Triggering **ERASE** for individual erase during a record or forward operation is an illegal operation and will be ignored. However, triggering **ERASE** for an individual erase operation during playback will delete the current played message, if it is the first or last one.

Figure 8.1: Global Erase Operation

## 8.2.5 Reset Operation

A 0.1  $\mu$ F capacitor is recommended to connect the  $\overline{\text{RESET}}$  to ground if a push button switch is used on this control. After  $\overline{\text{RESET}}$  is triggered, the device will be in power down state and place both the record and the playback pointers at the last message. When a microcontroller is used for a power-on-Reset,  $\overline{\text{RESET}}$  must stay active for at least 1  $\mu$ sec after all supply rails reach their proper specifications.

October 2006 - 25 - Revision 0

#### 8.2.6 VOL Operation

Pulsing  $\overline{\text{VOL}}$  Low changes the volume output. Each pulse on  $\overline{\text{VOL}}$  will decrease the volume until the minimum setting is reached. Subsequent pulses will increase the volume until the maximum level is reached and the cycle will start again. There are 8 steps of volume control. Each step changes the volume by 4 dB. The  $\overline{\text{VOL}}$  is debounced internally. A  $\overline{\text{RESET}}$  operation will re-initialize the volume level to the factory default state, which is the maximum level. One can change this default setting using related SPI command.

#### 8.2.7 FT (Feed-Through) Operation

The  $\overline{FT}$  controls the feed-through path from the input to the output of the chip. By factory default, when  $\overline{FT}$  is held Low, FT mode is enabled. Active FT mode will pass Analn signal to both SPK and AUD outputs when the device is idle. During recording, device will record the Analn signal into the memory.

However, the FT path is subject to the contents of NVCFG register during power-on-reset. Once power-up, one can configure the feed-through path by changing the setting of the APC register using the related SPI commands.

# 8.3 VALERT FEATURE (OPTIONAL)

If this optional feature is enabled, after a recording operation, the LED output will blink once every few seconds to indicate the presence of a new message, while the device is in power-down state. After any subsequent operations, which power-up the device, the vAlert will stop flashing.

#### **8.4 ANALOG INPUTS**

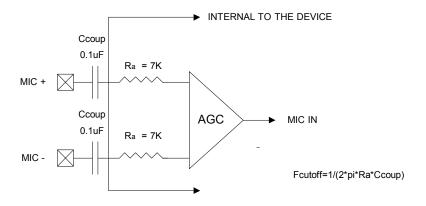

#### 8.4.1 Microphone Input

Figure 8.2: MIC input impedance (When this path is active)

October 2006 - 26 - Revision 0

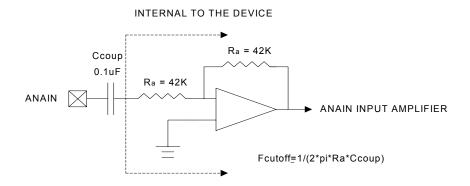

# 8.4.2 Analn Input

Figure 8.3: Analn input impedance (When the device is powered-up)

## 8.5 SYSTEM MANAGEMENT

While in Standalone mode, it is recommended the designer to utilize the feedback from the  $RDY/\overline{INT}$  pin, visual and optional SE indications for effective system management with respect to its operations.

October 2006 - 27 - Revision 0

# 9 CIRCULAR MEMORY ARCHITECTURE (CMA)

The ISD1700 has a built-in circular memory management protocol to handle message management internally in Standalone mode. Before the device attempts to access memory via push-button controls or the SPI equivalent commands, it checks the memory structure for conformity to this circular memory protocol. If it fails, the LED will flash seven times and the device accepts no commands except reset and global erase in standalone mode. The only way to recover from this condition is to perform a global erase function successfully.

The area of memory under circular memory management control is from address 0x010 to the end of memory, i.e. only for the voice message storage. This is because the first sixteen rows, up to address 0x00F are reserved for sound effects (SE). When the address pointer reaches the end of the memory, it will automatically roll over to address 0x010. To comply with the circular memory architecture, all messages must form a contiguous block with no empty space between them and there must be at least one blank row left between the last message and first message. This allows ISD1700 state machine to find the first and last message in memory after POR or Chk\_Mem command in SPI mode. This CMA is automatically implemented by the ISD1700 in standalone mode and the similar pushbutton SPI commands.

In SPI mode, however, the user has the option of direct addressing the array with the SET\_PLAY, SET\_REC and SET\_ERASE commands, which are capable of going around this structure. This is an advantage if the user wishes to implement a fragmented memory management scheme onto the ISD1700. These SET commands also permit the recording, playback and erasing the sound effects in SPI mode. The SET\_PLAY command can never corrupt the CMA, but the SET\_REC and SET\_ERASE commands have the ability to fragment the message memory area and invalidate the circular memory structure. Thus, if standalone operation or internal memory management is required, care must be taken in using these commands while in SPI mode.

October 2006 - 28 - Revision 0

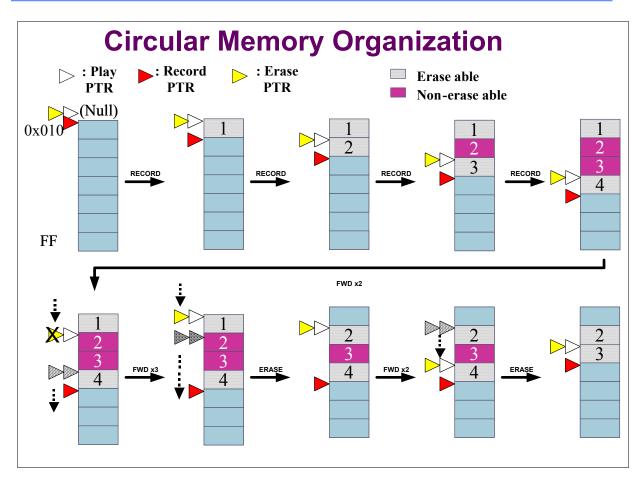

Figure 9.1 Circular Memory Management

An example of the Circular memory management is shown in Figure 9.1. Here the memory array starts with an empty memory, the ISD1700 detects this and sets the record pointer to point at row 0x010, the first row of normal memory. A subsequent REC command will record message 1. Now the playback pointer will point to the beginning of message 1 and the record pointer to the next row after message 1. Three more recordings will write message 2, 3 and 4. This results the record and playback pointers are at next row after message 4 and beginning of message 4, respectively. If two FWD commands are now sent, the playback pointer will jump from last message to message 1 then message 2. Note that the erase pointer is now invalid since erase is restricted to only the first or last message. If three FWD commands were executed, the playback pointer would end up back at message 1 after wrapping around the last message. Because the pointer is at the first message an erase command is valid. An ERASE will remove message 1 from the memory. Note that the record pointer has been unaffected by all these operations. A further two FWD and a subsequent ERASE commands will remove message 4.

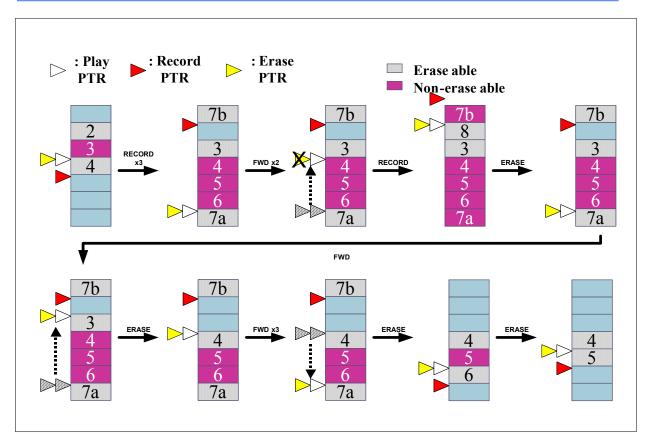

Figure 9.2 Further Circular Message Management

A Further example of circular memory management is shown in Figure 9.2. Here note how the three REC commands cause message 7 to be split across the end of memory boundary. Two FWD commands will wrap the playback pointer to message four – the second message in the circular queue. Now if we record until the memory is full, the record pointer becomes invalid and no further record commands will be accepted by the device. Either the first or last message must be erased first. The example above demonstrates erasing the last and then the first message as well.

## 9.1 RESTORING CIRCULAR MEMORY ARCHITECTURE

In case the circular memory architecture is damaged, the LED will blink seven times of duration  $T_{\mathsf{LErr}}$  when either  $\overline{\mathsf{REC}}$ ,  $\overline{\mathsf{PLAY}}$ ,  $\overline{\mathsf{ERASE}}$  or  $\overline{\mathsf{FWD}}$  button or alike SPI commands are activated. During such occurrence, the only way to recover back to an operating status is to perform a successful global erase operation. In order to perform this effectively, one has to press-and-hold the  $\overline{\mathsf{ERASE}}$  for approximately twelve seconds (time for LED to blink seven times plus period for global erase) at 8 kHz sampling frequency. As a result, the device will resume back to the normal condition. Details are shown in the related timing diagram.

October 2006 - 30 - Revision 0

# 10 SERIAL PERIPHERAL INTERFACE (SPI) MODE

#### 10.1 MICROCONTROLLER INTERFACE

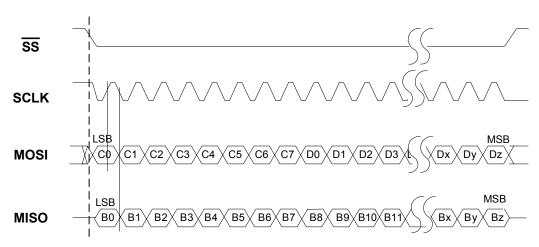

A four-wire (SCLK, MOSI, MISO &  $\overline{SS}$ ) SPI interface can be used for serial communication to the ISD1700 device. The ISD1700 Series is configured to operate as a peripheral slave device. All operations can be controlled through this SPI interface.

To allow compatibility with Standalone mode, some SPI commands: PLAY, REC, ERASE, FWD, RESET and G\_ERASE behave similarly as the corresponding features in Standalone mode. In addition, SET\_PLAY, SET\_REC and SET\_ERASE commands allow the user to specify the start and the end addresses of the operation. Besides, there are commands accessing the APC register, which controls the configuration of the analog paths used by the device, and etc.

#### 10.2 SPI INTERFACE OVERVIEW

The ISD1700 series operates via the SPI serial interface with the following protocol.

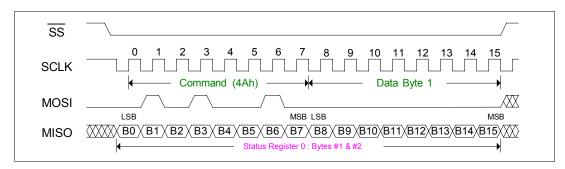

Data transfer protocol requires that the microcontroller's SPI shift registers are clocked out on the falling edge of the SCLK. The SPI protocol of the ISD1700 device is as follows: