Non ci sono prodotti a carrello.

Esaurito

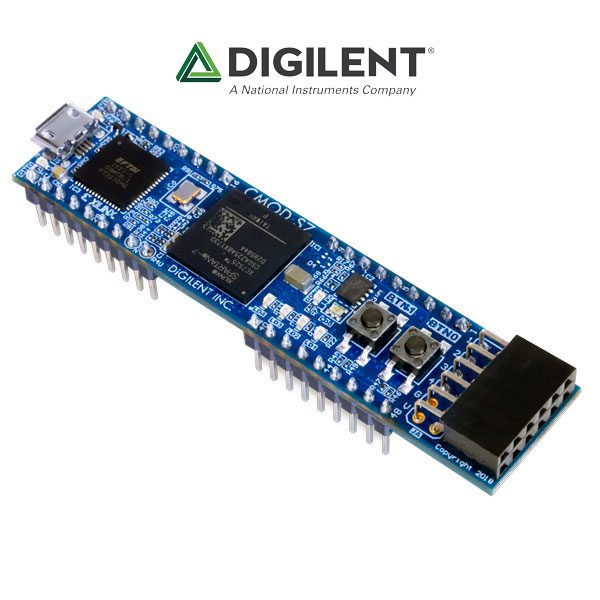

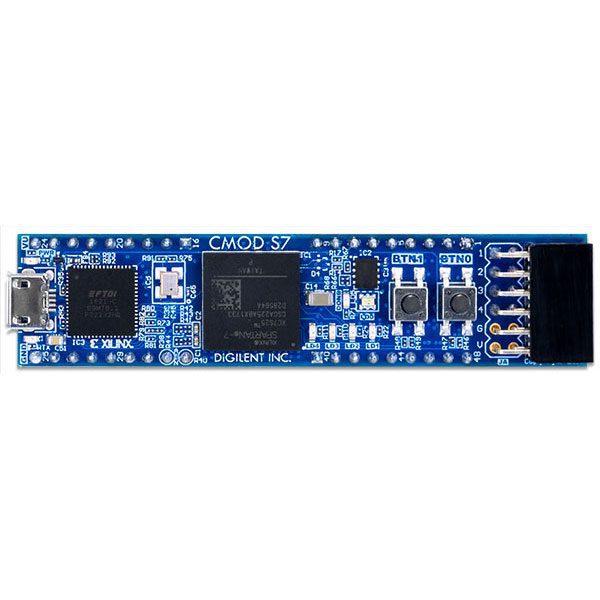

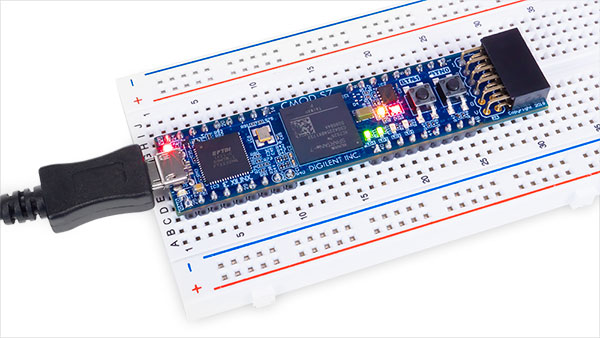

Digilent Cmod S7 è una piccola scheda basata sull’FPGA Xilinx Spartan-7 con fattore di forma DIP a 48 pin (pin totali presenti 36 pin)

|

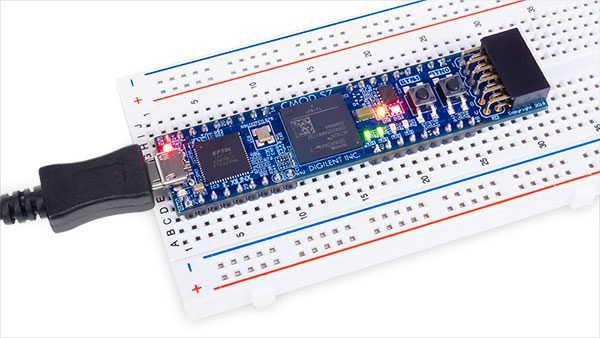

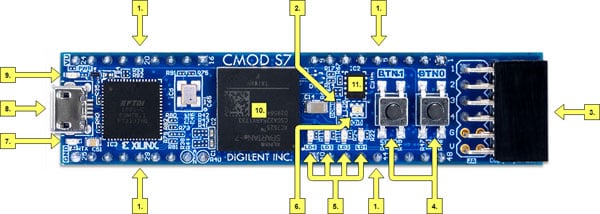

Digilent Cmod S7 è una piccola scheda basata sull’FPGA Xilinx Spartan-7 con fattore di forma DIP a 48 pin (pin totali presenti 36 pin). Dispone di 32 I/O (digitali) FPGA, 2 ingressi analogici 0-3,3V single-ended su XADC, 2 Pulsanti, 5 LED (4 normali e 1 RGB), rendendo il Cmod S7 ideale per l’uso con breadboard senza saldatura. Grazie alle sue dimensioni compatte può essere inserito in un socket standard e utilizzato in sistemi embedded. La scheda include anche una ROM di programmazione, una sorgente di clock, un circuito di programmazione e trasferimento dati USB, alimentatori, LED e pulsanti. Cmod S7 è pienamente compatibile con le versioni Vivado ® Design Suite 2018.1 e successive. È supportato dall’opzione di installazione gratuita WebPACK™, che non richiede una licenza, pertanto i progetti possono essere implementati senza costi aggiuntivi. Questa installazione gratuita include la possibilità di creare progetti di processori soft-core MicroBlaze™. Risorse di progettazione, progetti di esempio ed esercitazioni sono disponibili per il download nel Centro risorse di Cmod S7. N.B. Cmod S7 può essere utilizzato con Vivado 2017.4, ma le installazioni WebPACK di questa versione di Vivado potrebbero non contenere i file del dispositivo specifico FPGA Spartan-7 utilizzato su Cmod S7. Per ulteriori informazioni e per una soluzione vedere cliccare su questo link Xilinx Answer Record . |

||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||

| Specifiche tecniche | ||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||

| Documentazione e link utili | ||||||||||||||||||||||||||||